| USN |  |  |  |  |    |  |

|-----|--|--|--|--|----|--|

|     |  |  |  |  | -3 |  |

10ES32

## Third Semester B.E. Degree Examination, Dec.2018/Jan.2019 Analog Electronic Circuits

Time: 3 hrs.

Max. Marks:100

Note: Answer any FIVE full questions, selecting at least TWO full questions from each part.

## PART – A

- 1 a. Derive the expression for dynamic resistance of the diode. Determine the dynamic resistance of the diode when the diode current is 2mA. (06 Marks)

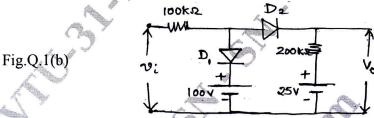

- b. The input voltage to the clipper circuit shown below in Fig.Q.1(b) varies linearly from 0 to 150 volts. Draw the transfer characteristics, indicate the slope and status of diode at each level. (08 Marks)

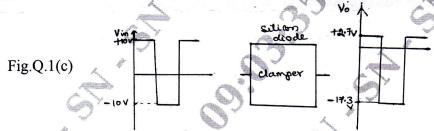

c. Design the clamper circuit for the input-output waveform shown in Fig.Q.1(c) using silicon diode. (06 Marks)

- 2 a. Derive the expression for the stability factor of the Emitter Bias circuit with respect to  $I_{CO}$  and  $V_{BE}$ . (06 Marks)

- b. How do you find the operating point of fixed Bias circuit?

(04 Marks)

- c. Design a voltage divider Bias circuit using a silicon transistor with B = 100 when  $V_{CC} = 12V$ ,  $V_{CE} = 6V$ ,  $I_C = 1mA$ , S = 20 and  $V_E = 1V$ . (10 Marks)

- 3 a. Derive the expression for the current gain, input impedance, voltage gain and output impedance for CE configuration using hybrid model. (10 Marks)

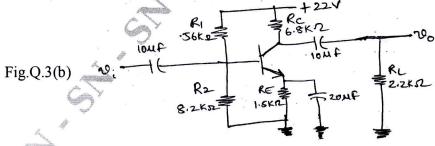

- b. Find  $r_e$ ,  $A_I$ ,  $Z_I$ ,  $A_V$  and  $Z_O$  for the amplifier circuit shown in Fig.Q.3(b) with B = 120 and  $r_o = 40 \text{K}\Omega$  (use  $r_e$  model). (10 Marks)

Determine the lower cut off frequencies f<sub>Li</sub> and f<sub>Lo</sub> for the circuit diagram shown in (06 Marks) Fig.Q.3(b) with  $R_S = 1K\Omega$ .

b. What is miller effect? Explain.

(06 Marks)

c. Determine the upper cut off frequencies fHi and fHo also fB and fT for the circuit shown in Fig.Q.3(b) given  $C_{\pi}(C_{be}) = 36 \text{ pF}$ ,  $C_{u}(C_{bc}) = 4 \text{pF}$   $C_{ce} = 1 \text{pF}$   $C_{wo} = 8 \text{pF}$   $C_{wi} = 6 \text{pF}$ .

(08 Marks)

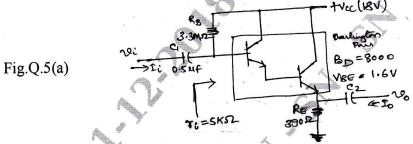

Calculate Z<sub>i</sub>, A<sub>i</sub>, A<sub>v</sub> and Z<sub>o</sub> of the Darlington pair shown in Fig.Q.5(a). Derive the formulas 5 (08 Marks) used.

What are the merits of feedback? What are different types of feedback connections?

(06 Marks)

Derive the expression for  $A_{\rm f}$ ,  $Z_{\rm if}$  and  $Z_{\rm of}$  for voltage shunt feedback circuit.

(06 Marks)

Explain the classification of power amplifiers.

(04 Marks)

- b. Explain how the efficiency of class A amplifiers increases from 25% to 50%. When we use transformer coupling.

- c. A class B power amplifier is delivering an output voltage of 10 volts peak to a  $8\Omega$  load. If the dc power supply is 30 volts, calculate:

- DC power input i)

- AC power delivered to the load ii)

- Conversion efficiency

- Power dissipated in the collector of each transistor.

(08 Marks)

- Derive the expression for frequency of oscillation of transistor phase shift oscillator. What is the value of current gain required for the loop gain to be greater than unity?

- With a neat circuit diagram, explain the working of the Hartley oscillator. Calculate the frequency of oscillation for C = 250 PF,  $L_1 = 1.5$  mH,  $L_2 = 1.5$  mH and M = 0.5 mH.

(10 Marks)

Write the ac equivalent model of JFET? Explain. 8

(04 Marks)

b. Derive the expression for Z<sub>i</sub>, Z<sub>o</sub>, and A<sub>v</sub> for common source JFET amplifier with fixed bias. (06 Marks)

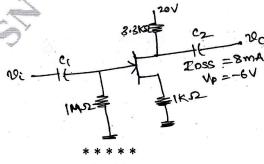

c. For the JFET amplifier shown in Fig.Q.8(c), the operating point is  $V_{GSQ} = -2.6V$  and  $I_{DQ} = 8mA$  with  $I_{DSS} = 8mA$  and  $V_P = -6V$ . The value of  $Y_{OS}$  is given as  $20\mu S$  determine: iv) calculate zo with and without rd iii) z<sub>i</sub> i) g<sub>m</sub>

without rd.

v) calculate A<sub>v</sub> with and (10 Marks)

2 of 2